Xyce 2-output pattern generator with positive pulse amplitude of 1V with transient analysis simulating an AHaH 1-2 synapse using the AHaH 1-2i (inverted) synapse subcircuit configured to produce the logic states of a 2-input OR gate.

Xyce 2-output pattern generator with positive pulse amplitude of 1V with transient analysis simulating an AHaH 1-2 synapse using the AHaH 1-2 synapse subcircuit configured to produce the logics state of a 2-input AND gate.

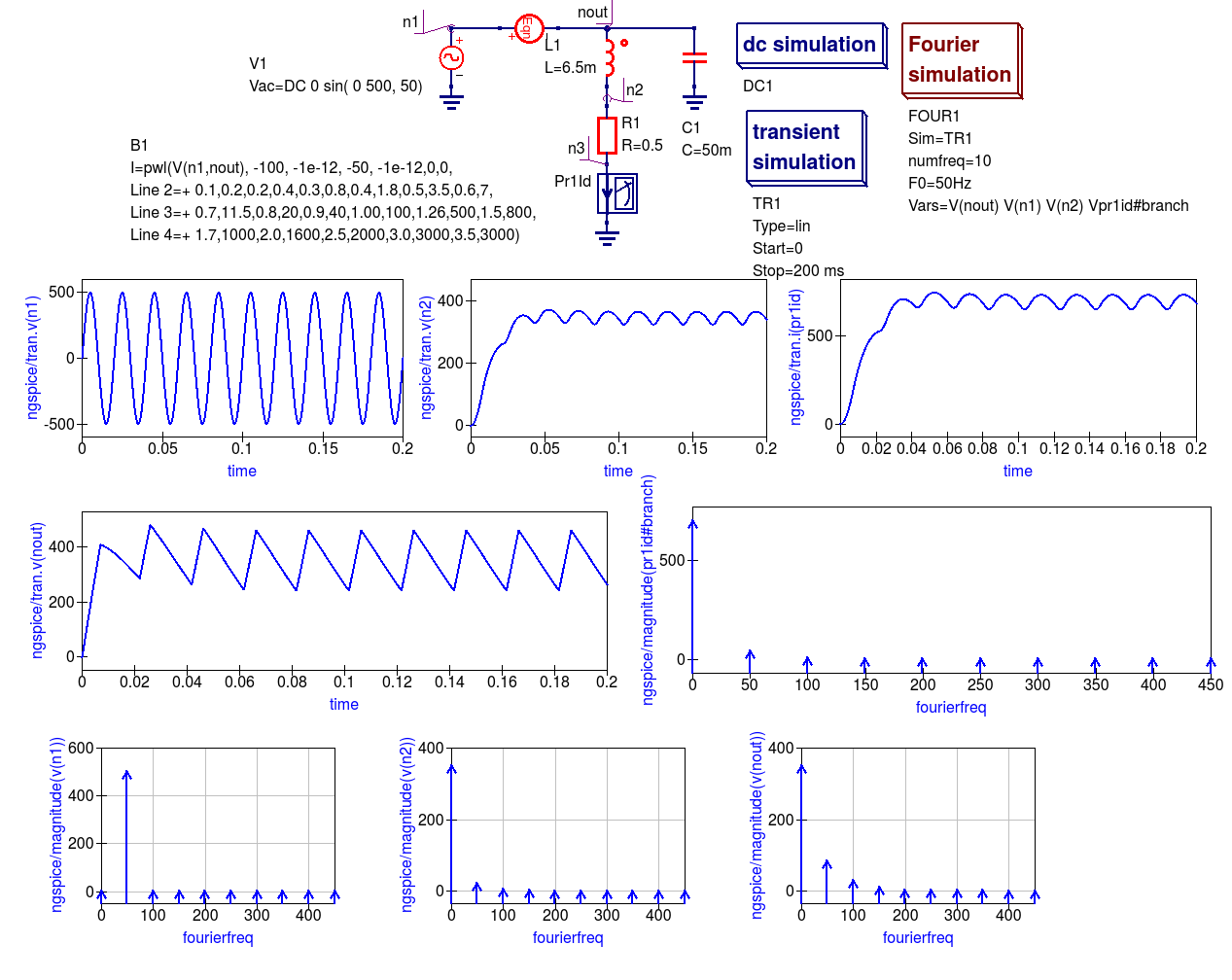

Xyce 2-output pattern generator with positive pulse amplitude of 1V with transient analysis simulating an AHaH 1-2 synapse using discrete memristor elements configured to produce the logic states of a 2-input OR gate. Xyce 2-output pattern generator with positive pulse amplitude of 1V with transient analysis simulating an AHaH 1-2 synapse using discrete memristor elements configured to produce the logic states of a 2-input AND gate. (2) Rectangular Pulse sources with positive pulse amplitude of 1V with transient analysis simulating an AHaH 1-2 synapse using discrete memristor elements configured to produce the logic states of a 2-input AND gate. Memristor Experiments Included in the Accompanying Examples The following experiments are included in the example Qucs-S project AHaH_Logic_prj available in the examples_knowm_oss-eda-0.0.19s-rc3 bundle. This new library will be used in future simulations of neuromemristive circuits and machine learning algorithms in hardware.Īn example Qucs-S project has been created to perform various experiments that we will later set up on actual memristor devices using the Knowm Memristor Discovery board and associated extender modules. The new Knowm_AHaH library included in the latest release candidate #3 of the Knowm OSS EDA Stack provides AHaH synapse node configurations implemented as sub-circuits to simplify building netlists for simulating the same basic logic circuits designed using discrete memristor components. As part of this tutorial we will also be exploring some additional advanced features of Qucs-S and Xyce for displaying timing diagrams and measuring the power across the memristor elements during the transient simulation.

QUCS SIMULATION STUCK HOW TO

I will demonstrate how to configure mixed mode simulations using a 2-output pattern generator contained in the Qucs-S Xyce Digital library to configure square wave pulses with specific pulse timing to produce the truth table inputs to the logic circuits. 2-input AND, 2-input OR gates) and perform simulations using discrete memristor elements and sub-circuit models which implement neuromemristive synapses (i.e. In this post I will continue to explore this behavior by creating basic logic cicuits (i.e. In a recent post titled Simulating the Knowm M-MSS Memristor Model Pulse Response with Qucs-S and Xyce, I presented circuit simulations that focus on the dynamic behavior of the M-MSS model’s incremental conductance response to applied square wave pulses.

0 kommentar(er)

0 kommentar(er)